Home › Forums › Mastering STM32 book support forum › ARM Semihosting example not working

- This topic has 2 replies, 2 voices, and was last updated 6 years, 7 months ago by

madmax.

-

AuthorPosts

-

June 16, 2019 at 2:19 pm #11784

hl1oap

ParticipantHello,

I am going through instructions in the book, and faced an issue at the early stage : example in chapter 5.2.1

I believe I followed all the instructions in the chapter regarding the ARM semihosting.

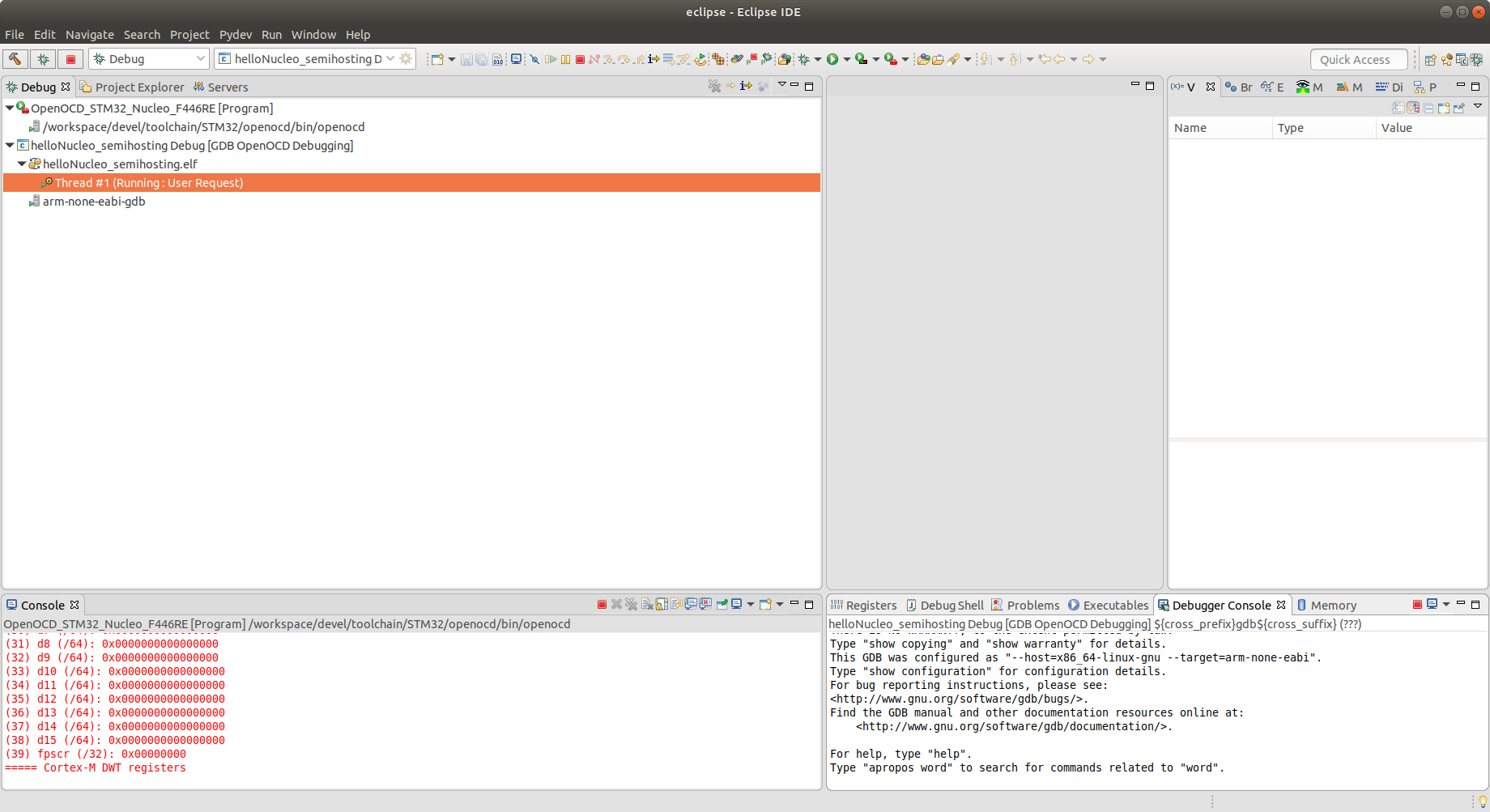

When I build the project and run the debug, the console output does not show the ‘Hello STM32 lovers!’ message like the Figure 18 in the book, but it stops at the sequence number ’39’ as follows;123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960616263646566676869707172737475767778GNU MCU Eclipse OpenOCD, 64-bitOpen On-Chip Debugger 0.10.0+dev-00593-g23ad80df4 (2019-04-22-20:18)Licensed under GNU GPL v2For bug reports, readhttp://openocd.org/doc/doxygen/bugs.htmlInfo : The selected transport took over low-level target control. The results might differ compared to plain JTAG/SWDadapter speed: 2000 kHzadapter_nsrst_delay: 100none separatesrst_only separate srst_nogate srst_open_drain connect_deassert_srstInfo : Listening on port 6666 for tcl connectionsInfo : Listening on port 4444 for telnet connectionsInfo : clock speed 2000 kHzInfo : STLINK V2J34M25 (API v2) VID:PID 0483:374BInfo : Target voltage: 3.260407Info : stm32f4x.cpu: hardware has 6 breakpoints, 4 watchpointsInfo : Listening on port 3333 for gdb connectionsInfo : accepting 'gdb' connection on tcp/3333Info : device id = 0x10006421Info : flash size = 512 kbytesInfo : flash size = 512 bytesInfo : Unable to match requested speed 2000 kHz, using 1800 kHzInfo : Unable to match requested speed 2000 kHz, using 1800 kHzadapter speed: 1800 kHztarget halted due to debug-request, current mode: ThreadxPSR: 0x01000000 pc: 0x080002d8 msp: 0x20020000Info : Unable to match requested speed 8000 kHz, using 4000 kHzInfo : Unable to match requested speed 8000 kHz, using 4000 kHzadapter speed: 4000 kHzsemihosting is enabledInfo : Unable to match requested speed 2000 kHz, using 1800 kHzInfo : Unable to match requested speed 2000 kHz, using 1800 kHzadapter speed: 1800 kHztarget halted due to debug-request, current mode: ThreadxPSR: 0x01000000 pc: 0x080002d8 msp: 0x20020000, semihosting===== arm v7m registers(0) r0 (/32): 0x00000000(1) r1 (/32): 0x00000000(2) r2 (/32): 0x00000000(3) r3 (/32): 0x00000000(4) r4 (/32): 0x00000000(5) r5 (/32): 0x00000000(6) r6 (/32): 0x00000000(7) r7 (/32): 0x00000000(8) r8 (/32): 0x00000000(9) r9 (/32): 0x00000000(10) r10 (/32): 0x00000000(11) r11 (/32): 0x00000000(12) r12 (/32): 0x00000000(13) sp (/32): 0x20020000(14) lr (/32): 0xFFFFFFFF(15) pc (/32): 0x080002D8(16) xPSR (/32): 0x01000000(17) msp (/32): 0x20020000(18) psp (/32): 0x00000000(19) primask (/1): 0x00(20) basepri (/8): 0x00(21) faultmask (/1): 0x00(22) control (/2): 0x00(23) d0 (/64): 0x0000000000000000(24) d1 (/64): 0x0000000000000000(25) d2 (/64): 0x0000000000000000(26) d3 (/64): 0x0000000000000000(27) d4 (/64): 0x0000000000000000(28) d5 (/64): 0x0000000000000000(29) d6 (/64): 0x0000000000000000(30) d7 (/64): 0x0000000000000000(31) d8 (/64): 0x0000000000000000(32) d9 (/64): 0x0000000000000000(33) d10 (/64): 0x0000000000000000(34) d11 (/64): 0x0000000000000000(35) d12 (/64): 0x0000000000000000(36) d13 (/64): 0x0000000000000000(37) d14 (/64): 0x0000000000000000(38) d15 (/64): 0x0000000000000000(39) fpscr (/32): 0x00000000===== Cortex-M DWT registersI got a feeling that the compiled binary image was not actually downloaded to the target board because;

1. The eclipse (in the debug perspective) does not show the source code. It is supposed to run up to the main function and halt at main.

2. The board is running the previous code I flashed before, even when the eclipse saids the Thread of new binary is Running.I attached the entire project file and screenshot of the eclipse when I ran the project.

For your information,

– OS : Ubuntu 18.04 with kernel version 4.15.0-51-generic

– Eclipse version : 2019-03 (4.11.0) (build ID 20190314-1200)If there is anybody having a clue on this issue, please help me. 🙂

Regards,

Arnold.

-

This topic was modified 6 years, 11 months ago by

hl1oap.

-

This topic was modified 6 years, 11 months ago by

hl1oap.

Attachments:

You must be logged in to view attached files.June 16, 2019 at 2:22 pm #11790hl1oap

ParticipantMy project file cannot be uploaded.

Let me try with this following up post.p.s.

It keeps making upload errors. I don’t know why. 🙁-

This reply was modified 6 years, 11 months ago by

hl1oap.

October 18, 2019 at 11:49 pm #12272madmax

ParticipantI am having the exact same issue.. Did you manage to resolve it ? Any help would be appreciated

Thanks in advance !!

This is how the output from the opnocd looks like

xPack OpenOCD, 64-bit Open On-Chip Debugger 0.10.0+dev (2019-07-17-11:28)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : The selected transport took over low-level target control. The results might differ compared to plain JTAG/SWD

srst_only separate srst_nogate srst_open_drain connect_deassert_srstInfo : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : clock speed 1000 kHz

Info : STLINK V2J33S0 (API v2) VID:PID 0483:3748

Info : Target voltage: 2.888208

Info : stm32f3x.cpu: hardware has 6 breakpoints, 4 watchpoints

Info : Listening on port 3333 for gdb connections

Info : accepting ‘gdb’ connection on tcp/3333

Info : device id = 0x10036422

Info : flash size = 256kbytes

Info : Unable to match requested speed 1000 kHz, using 950 kHz

Info : Unable to match requested speed 1000 kHz, using 950 kHz

target halted due to debug-request, current mode: Thread

xPSR: 00000000 pc: 0xfe32f000 msp: 0xb083b500

Info : Unable to match requested speed 8000 kHz, using 4000 kHz

Info : Unable to match requested speed 8000 kHz, using 4000 kHz

semihosting is enabledInfo : Unable to match requested speed 1000 kHz, using 950 kHz

Info : Unable to match requested speed 1000 kHz, using 950 kHz

target halted due to debug-request, current mode: Thread

xPSR: 00000000 pc: 0xfe32f000 msp: 0xb083b500, semihosting

Info : Unable to match requested speed 8000 kHz, using 4000 kHz

Info : Unable to match requested speed 8000 kHz, using 4000 kHz

Info : Unable to match requested speed 1000 kHz, using 950 kHz

Info : Unable to match requested speed 1000 kHz, using 950 kHz

target halted due to debug-request, current mode: Thread

xPSR: 00000000 pc: 0xfe32f000 msp: 0xb083b500, semihosting

Info : Unable to match requested speed 1000 kHz, using 950 kHz

Info : Unable to match requested speed 1000 kHz, using 950 kHz

target halted due to debug-request, current mode: Thread

xPSR: 00000000 pc: 0xfe32f000 msp: 0xb083b500, semihosting

===== arm v7m registers

(0) r0 (/32): 0x00000000

(1) r1 (/32): 0x00000000

(2) r2 (/32): 0x00000000

(3) r3 (/32): 0x00000000

(4) r4 (/32): 0x00000000

(5) r5 (/32): 0x00000000

(6) r6 (/32): 0x00000000

(7) r7 (/32): 0x00000000

(8) r8 (/32): 0x00000000

(9) r9 (/32): 0x00000000

(10) r10 (/32): 0x00000000

(11) r11 (/32): 0x00000000

(12) r12 (/32): 0x00000000

(13) sp (/32): 0xB083B500

(14) lr (/32): 0xFFFFFFFF

(15) pc (/32): 0xFE32F000

(16) xPSR (/32): 0x00000000

(17) msp (/32): 0xB083B500

(18) psp (/32): 0x00000000

(19) primask (/1): 0x00

(20) basepri (/8): 0x00

(21) faultmask (/1): 0x00

(22) control (/2): 0x00

(23) d0 (/64): 0x0000000000000000

(24) d1 (/64): 0x0000000000000000

(25) d2 (/64): 0x0000000000000000

(26) d3 (/64): 0x0000000000000000

(27) d4 (/64): 0x0000000000000000

(28) d5 (/64): 0x0000000000000000

(29) d6 (/64): 0x0000000000000000

(30) d7 (/64): 0x0000000000000000

(31) d8 (/64): 0x0000000000000000

(32) d9 (/64): 0x0000000000000000

(33) d10 (/64): 0x0000000000000000

(34) d11 (/64): 0x0000000000000000

(35) d12 (/64): 0x0000000000000000

(36) d13 (/64): 0x0000000000000000

(37) d14 (/64): 0x0000000000000000

(38) d15 (/64): 0x0000000000000000

(39) fpscr (/32): 0x00000000

===== Cortex-M DWT registers-

This reply was modified 6 years, 7 months ago by

madmax.

-

This topic was modified 6 years, 11 months ago by

-

AuthorPosts

- You must be logged in to reply to this topic.